[Linux]时钟源-基于S3C2440

[Linux]时钟源-基于S3C2440

Linux学习总结

艾恩凝 2021/3/25

一、时钟功能描述

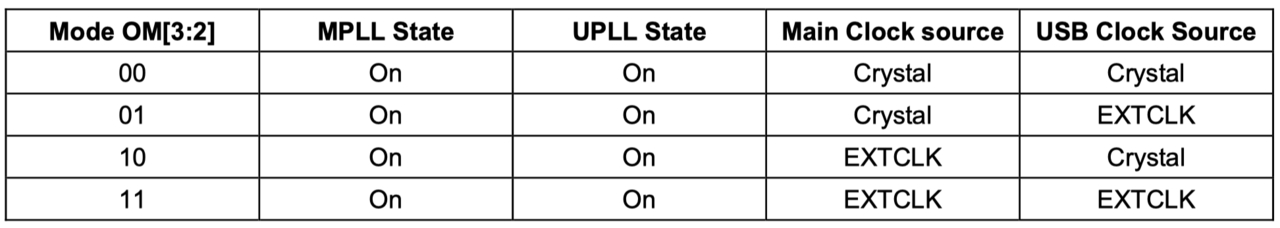

1)时钟源选择

上表说明了该芯片对时钟源的支持,查看原理图后,OM[3:2]为00,选择了12MHz的时钟源。

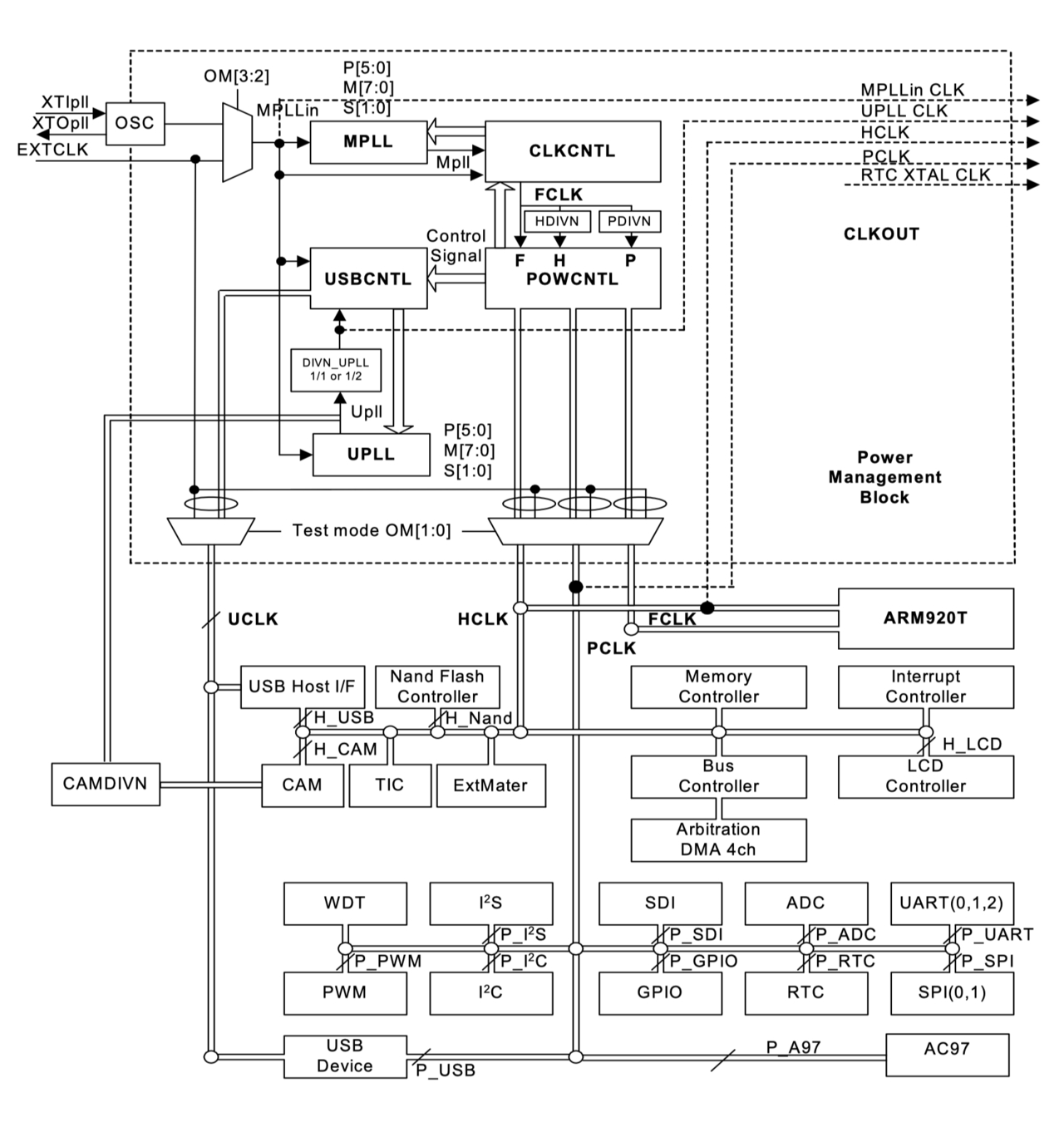

2)时钟发生框图

上图中说明了晶振的经过,首先经过MPLL,生成FLK,之后是HCLK,PCLK,这三种时钟速度不同.

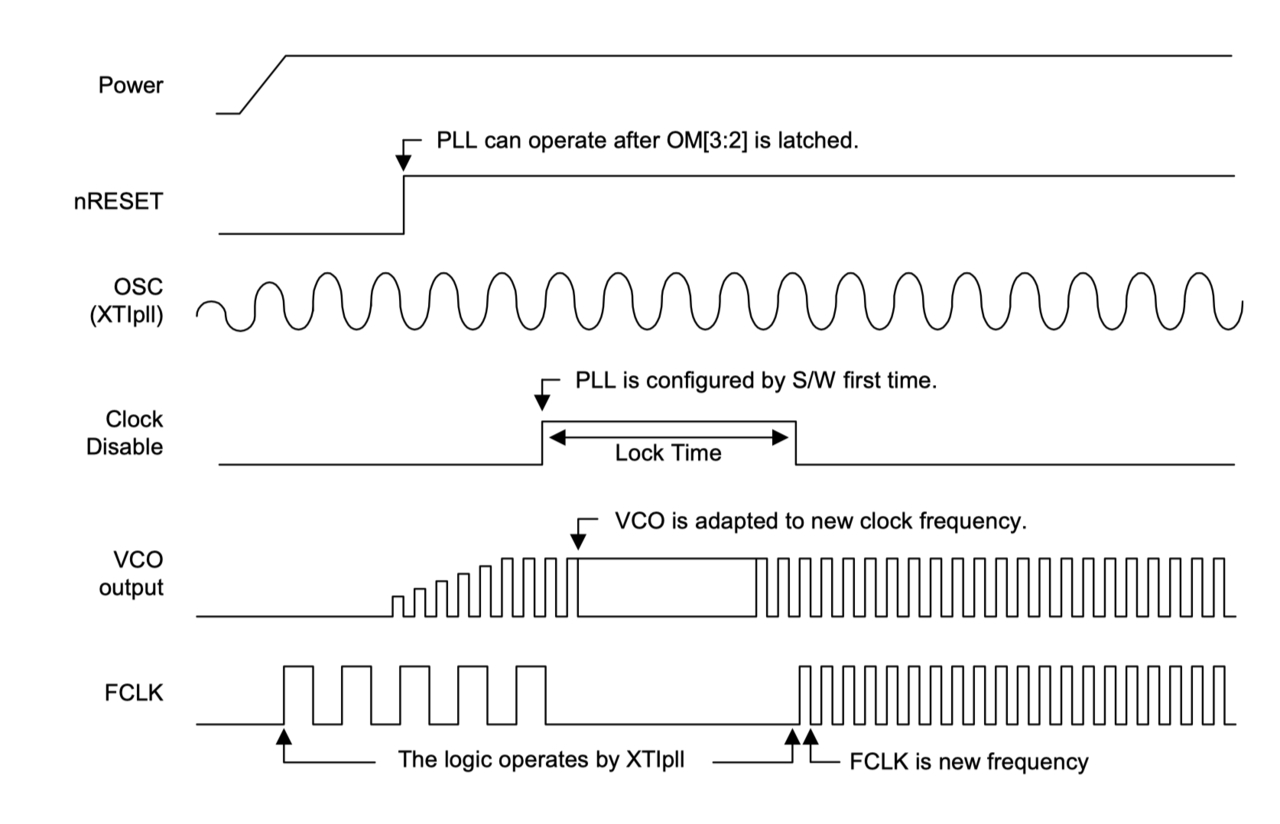

3)上电复位

上图说明,在上电以后,复位首先不会进行复位,而是等待电源稳定后进行复位,FCLK在上电后就会产生设置频率,当复位之后,PLL进行设置,现在就会进行锁定,cpu和FCLK都不会进行工作,在设置完毕后,并且锁定时间到了之后,FCLK和cpu会用新设置的时钟频率进行工作。

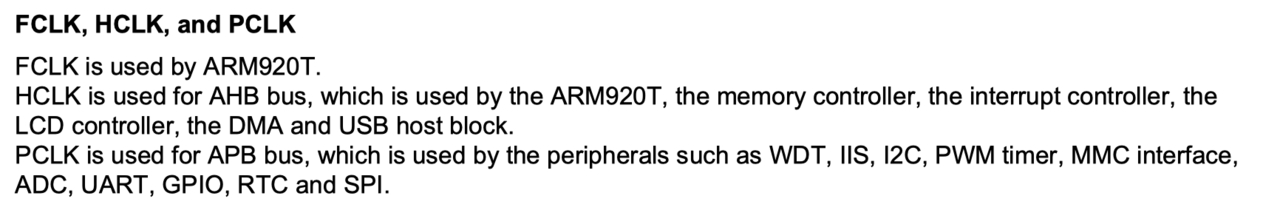

4)FCLK,HCLK,and PCLK

FCLK,高速,用来供给cpu使用,最高可达400MHz

HCLK,用于AHB总线,存储控制器,中断控制器,DMA等,最高可达136MHz

PCLK,用于APB总线,像ADC,UART,GPIO,SPI,I2C之类的低速设备,最高可达68MHz

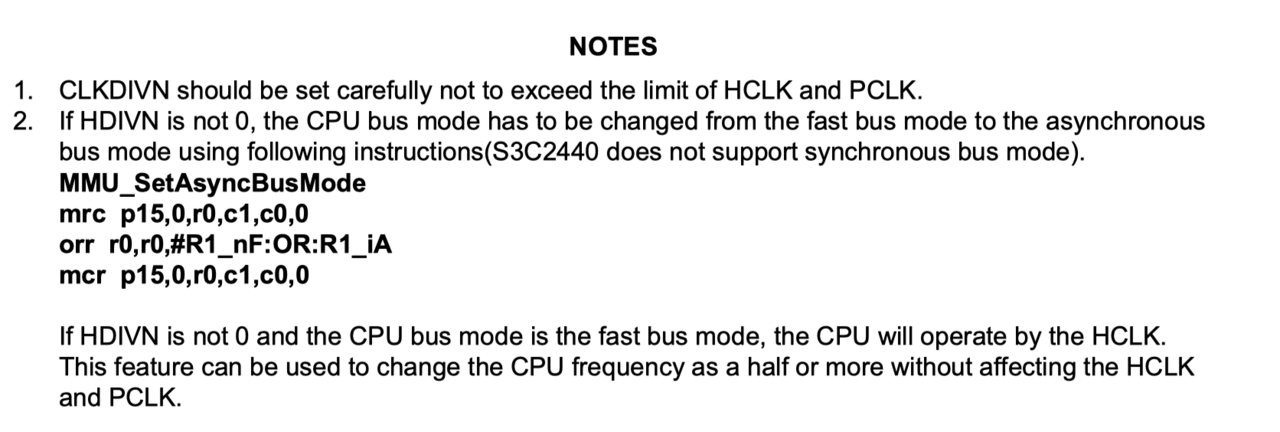

5)注意事项

如果当HDIVN不设置为0,我们要设置成异步模式,否则cpu就会使用HCLK频率进行工作了。

二、时钟设置

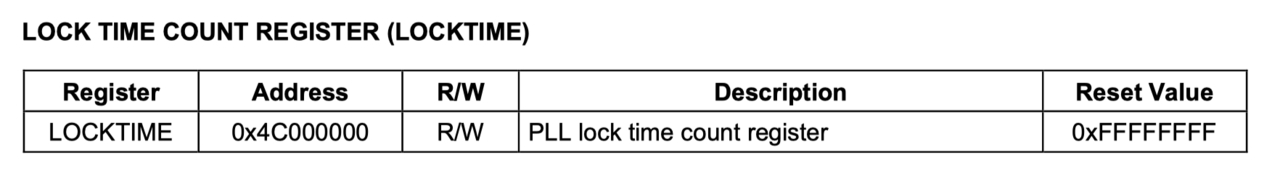

1)锁定时间

上图说明了设置锁定时间地址,和默认时间

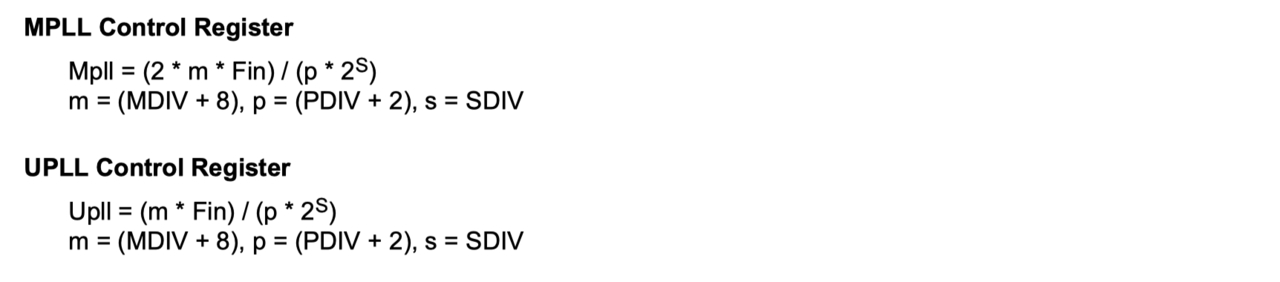

2)计算公式

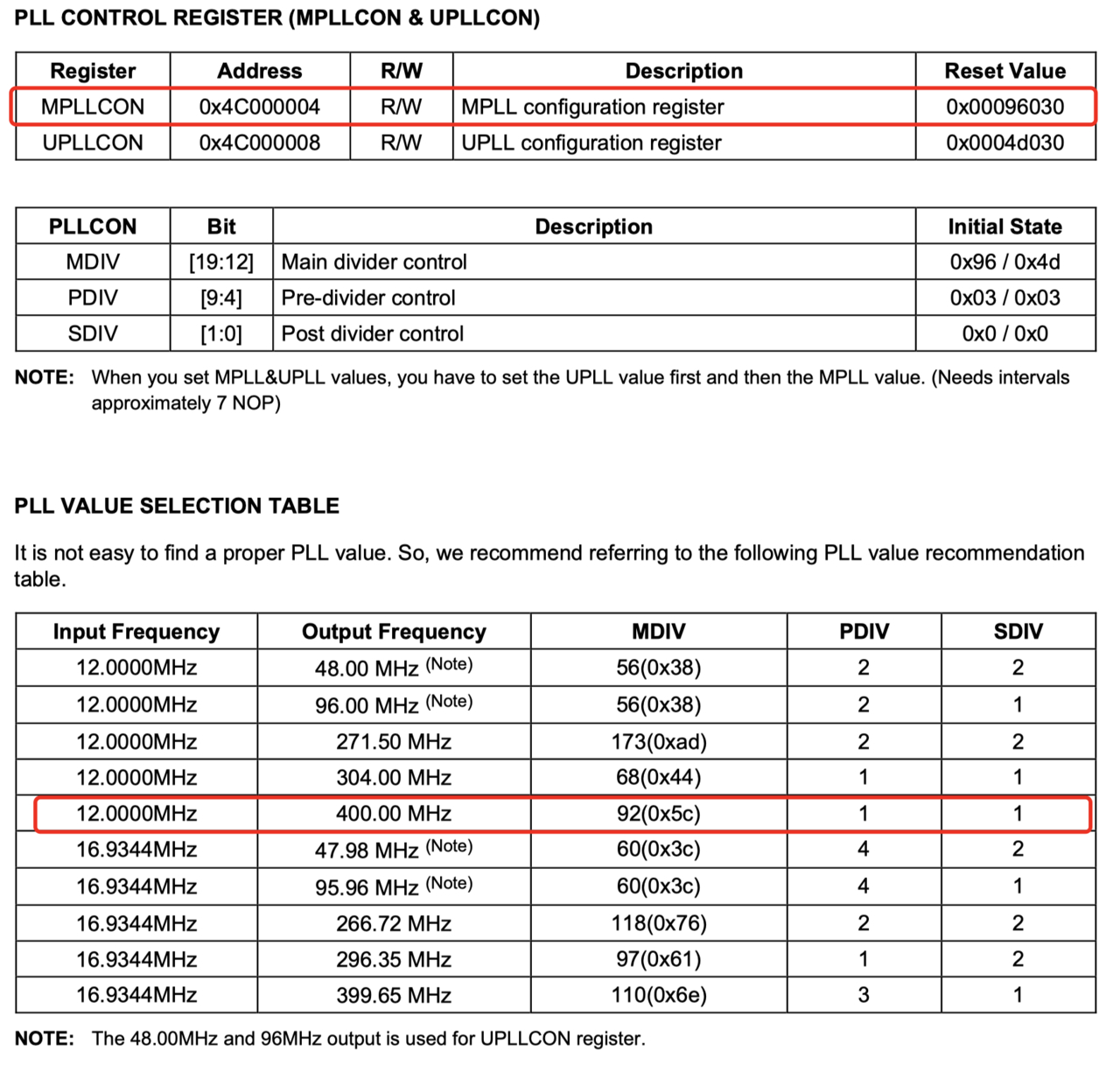

3)MPLL说明

图中表述了设置MPLL的地址和需要设置的值

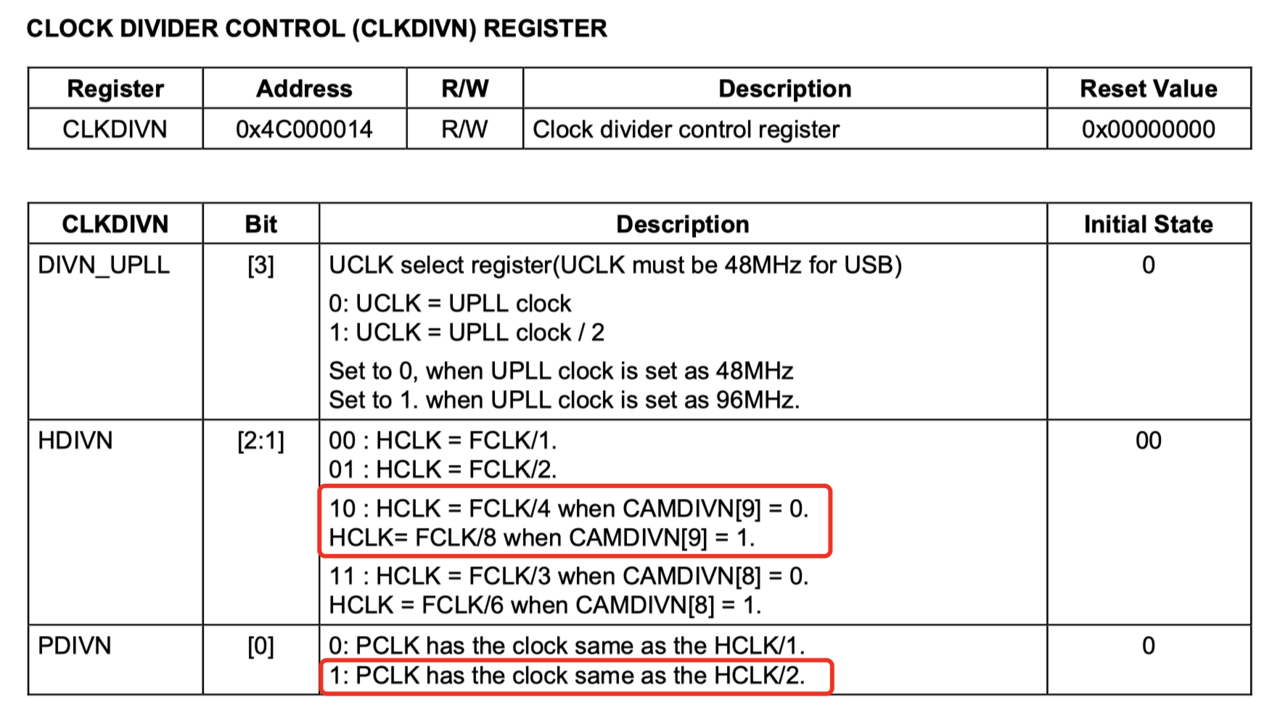

4)CLKDIVN说明

图中表述了设置CLKDIVN的地址,根据需要进行设置

三、汇编代码实现

1/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

2 /* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

3 ldr r0, =0x4C000000

4 ldr r1, =0xFFFFFFFF

5 str r1, [r0]

6

7 /* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

8 ldr r0, =0x4C000014

9 ldr r1, =0x5

10 str r1, [r0]

11

12 /* 设置CPU工作于异步模式 */

13 mrc p15,0,r0,c1,c0,0

14 orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

15 mcr p15,0,r0,c1,c0,0

16

17 /* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

18 * m = MDIV+8 = 92+8=100

19 * p = PDIV+2 = 1+2 = 3

20 * s = SDIV = 1

21 * FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

22 */

23 ldr r0, =0x4C000004

24 ldr r1, =(92<<12)|(1<<4)|(1<<0)

25 str r1, [r0]

26

27 /* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

28 * 然后CPU工作于新的频率FCLK

29 */

上述代码在start.S中,初始化裸板程序时。

吾心信其可行,

则移山填海之难,

终有成功之日!

——孙文

则移山填海之难,

终有成功之日!

——孙文

评论

评论

0 评论